About Me

I'm applying for a Ph.D. position in EECS/ECE, Fall 2023.

Please feel free to contact me for further discussions!

E-mail: itlin0611@gmail.com

Authors: I-T. Lin, Z.-S. Fu, W.-C. Chen, L.-Y. Lin, N.-S. Chang, C.-P. Lin, C.-S. Chen,

C.-H. Yang.

Accepted by International Solid-State Circuits Conference

(ISSCC) 2023.

Details are coming soon!

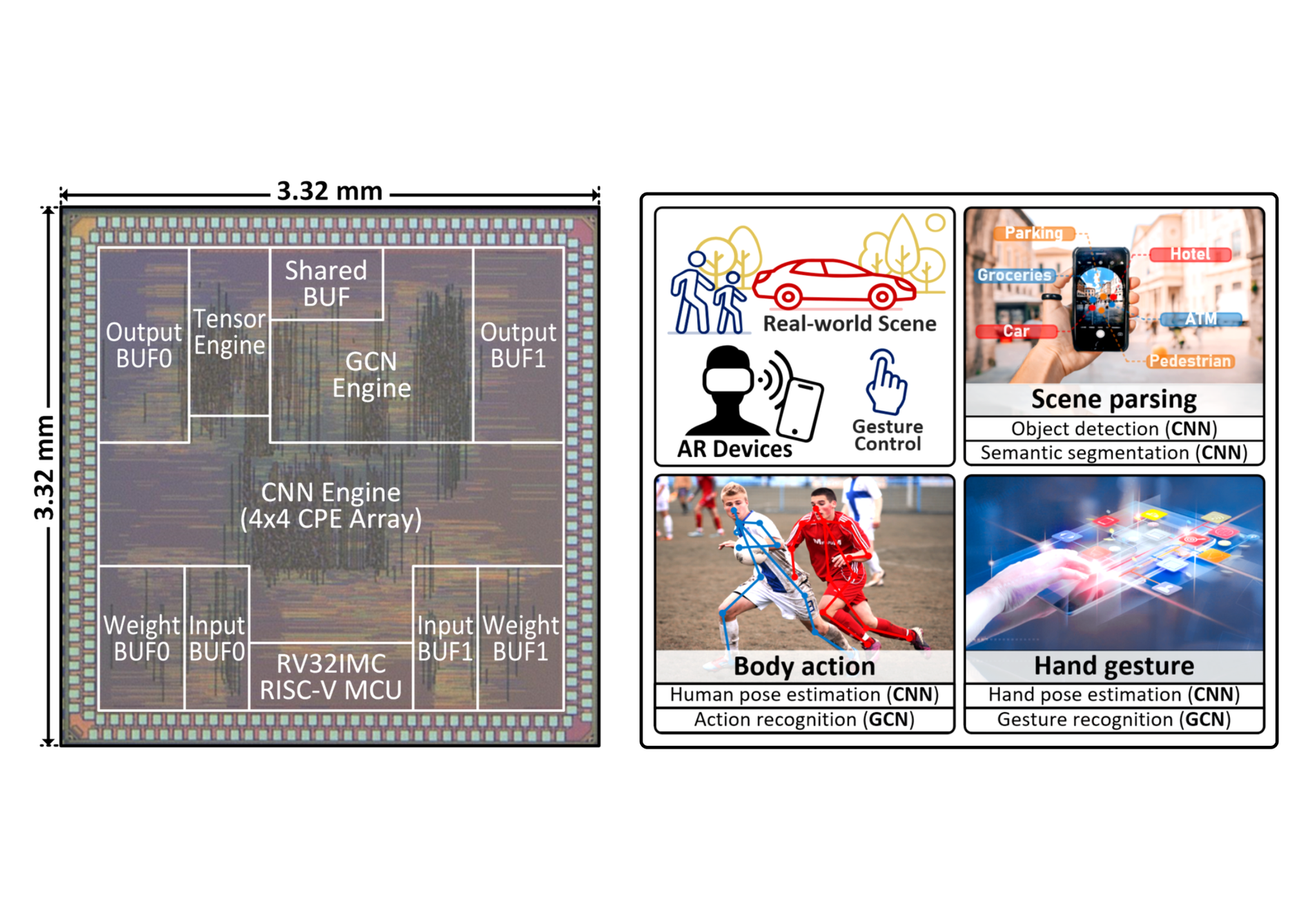

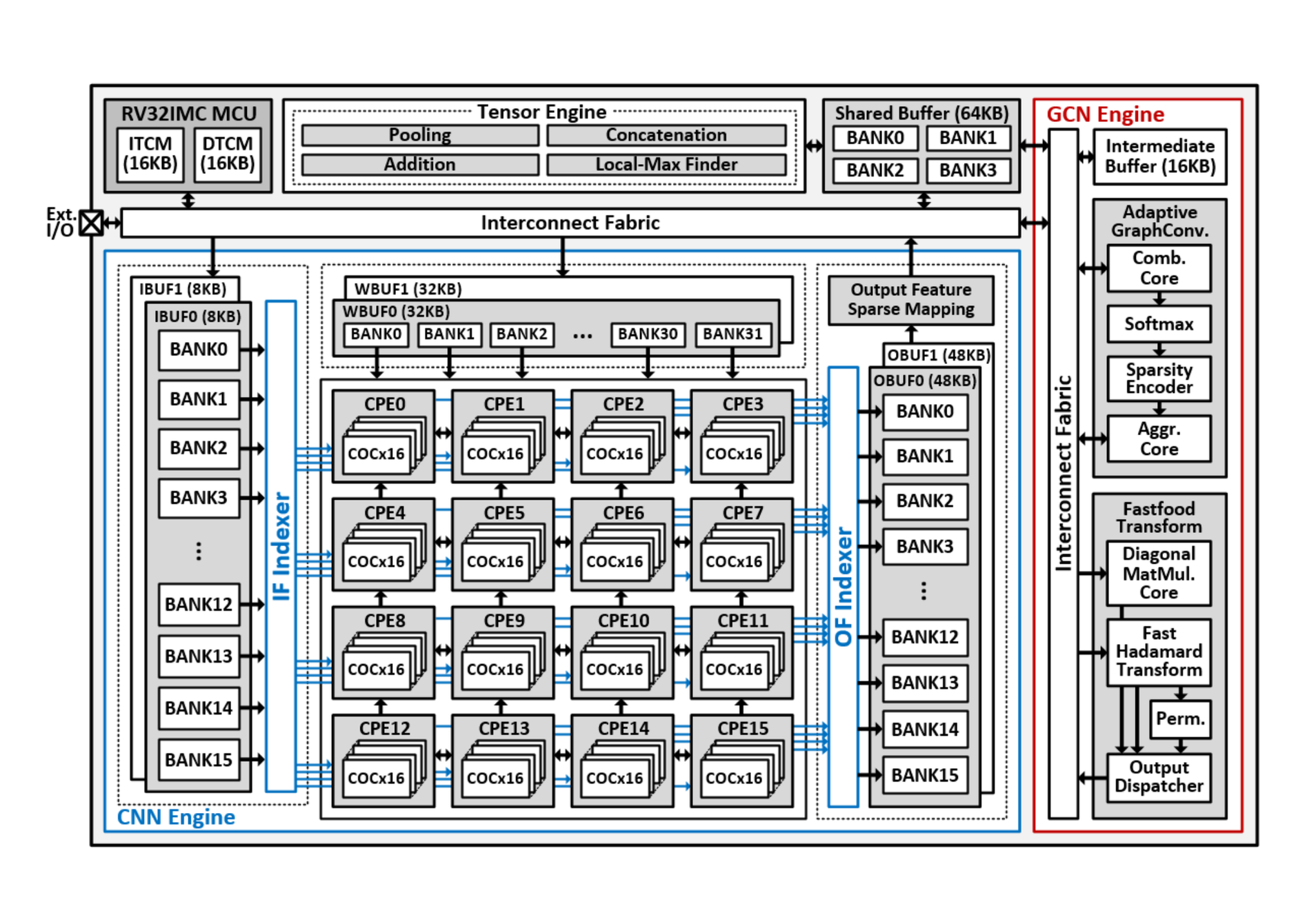

Authors: W.-C. Huang, I-T. Lin, W.-C. Chen, L.-Y. Lin, N.-S. Chang, C.-P. Lin, C.-S. Chen,

C.-H. Yang.

Published in International Symposium on VLSI Circuits

(VLSI Circuits) 2022.

This work presents the first CNN-GCN SoC for diverse AI vision computations on mobile augmented reality (AR). The SoC outperforms prior CNN accelerators by 2x in energy efficiency and prior action recognition processor by 18x in latency.

Link to paper

NTU | Sep. 2020 - present | Advisor: Prof. Chia-Hsiang Yang

I mainly work on domain-specific hardware acceleration and algorithm-hardware co-design.

Selected Projects:

- Motion-Control SoC for Autonomous Mobile Robots

- Deep Learnining SoC for Mobile Augmented Reality

- Hardware-Aware Neural Network Quantization

New Taipei City, Taiwan | Aug. 2019

I was responsible to build a visual-searching testing system, incorporating Ganzin eye-tracking solution, for detecting and evaluating possible visual field loss

NTU | Sep. 2018 - June 2019 | Advisor: Prof. Shao-Yi Chien

I worked on mobile deep learning and developed an automatic workflow to deploy CNNs on Android mobile phones

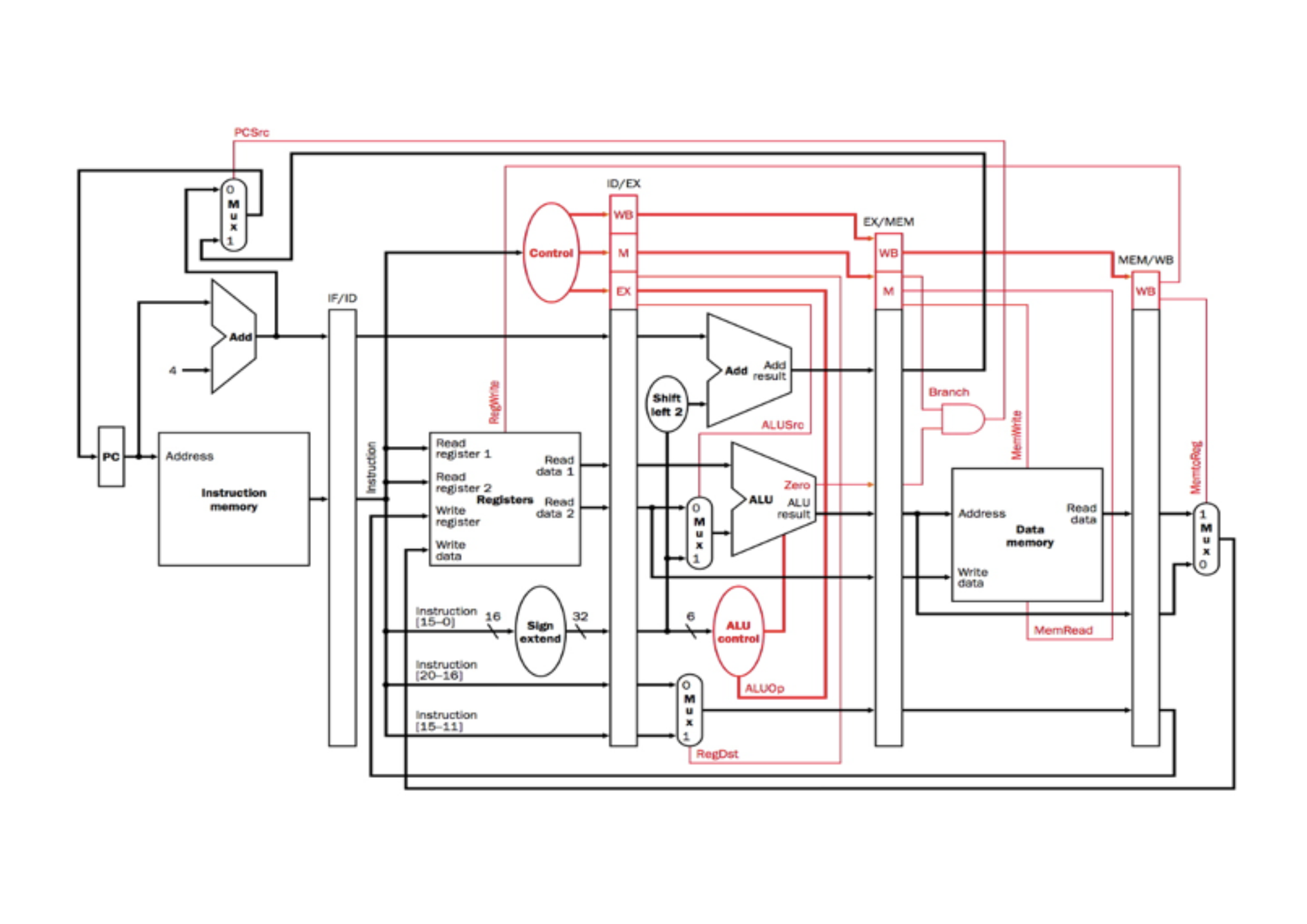

- Proposed a trajectory optimization accelerator

- Interated an ARM Cortex-M3 MCU

- Taped-out in 28nm CMOS technology

- Accepted by ISSCC'23

- Integrated a CNN Engine, a GCN Engine, and a RISC-V MCU

- Taped-out in 28nm CMOS technology

- Published in VLSI'22

- Proposed a two-stage 4-bit quantization scheme

- Optimized quantized convolution for efficient HW design

- Honored by 2020 Delta Young Talent Award

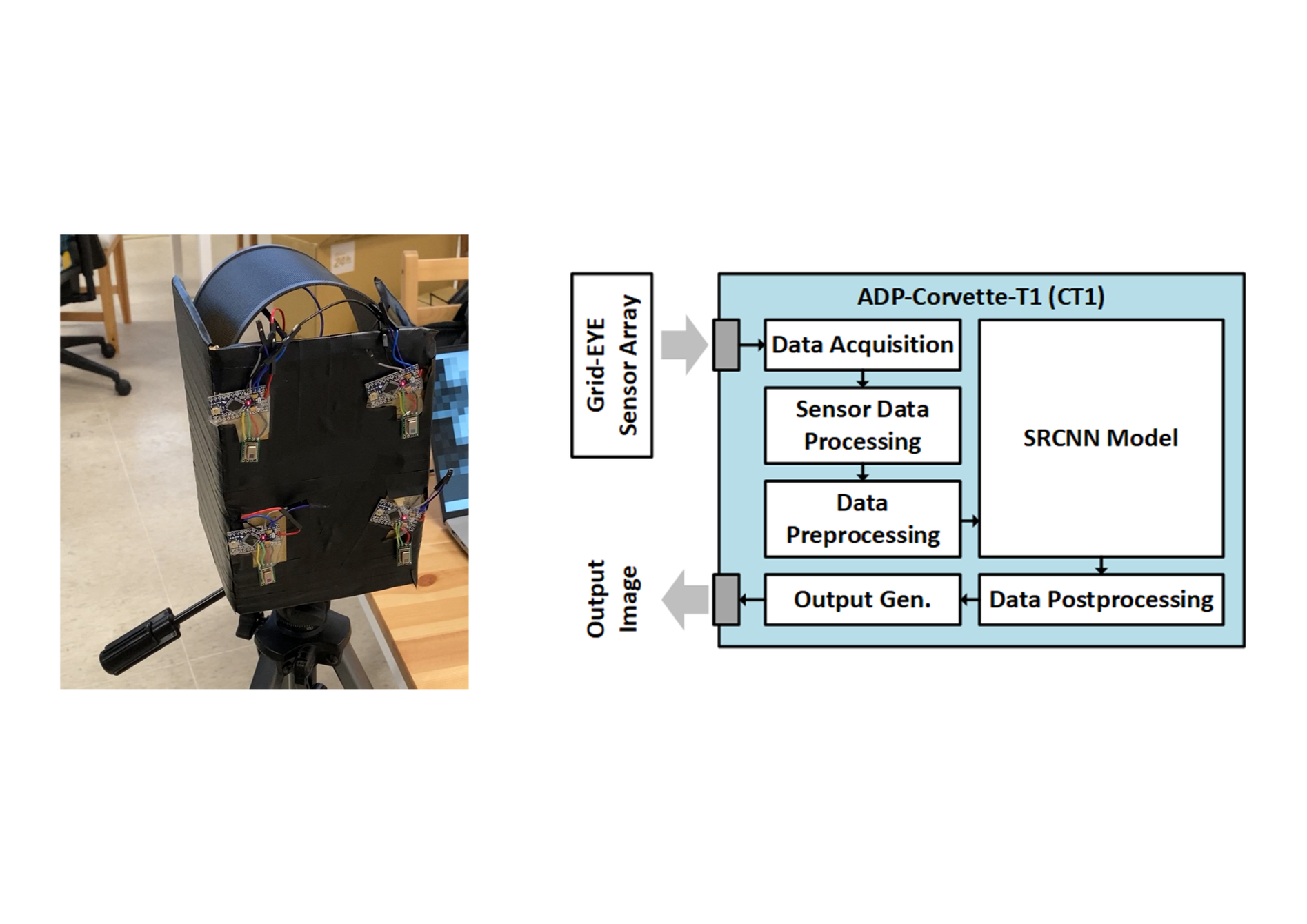

- Incorporated 4 ultra-low-resolution thermal sensors

- Optimized a thermal image SRCNN for ADP-Corvette-T1

- Currently the finalist of 2022 Andes Award

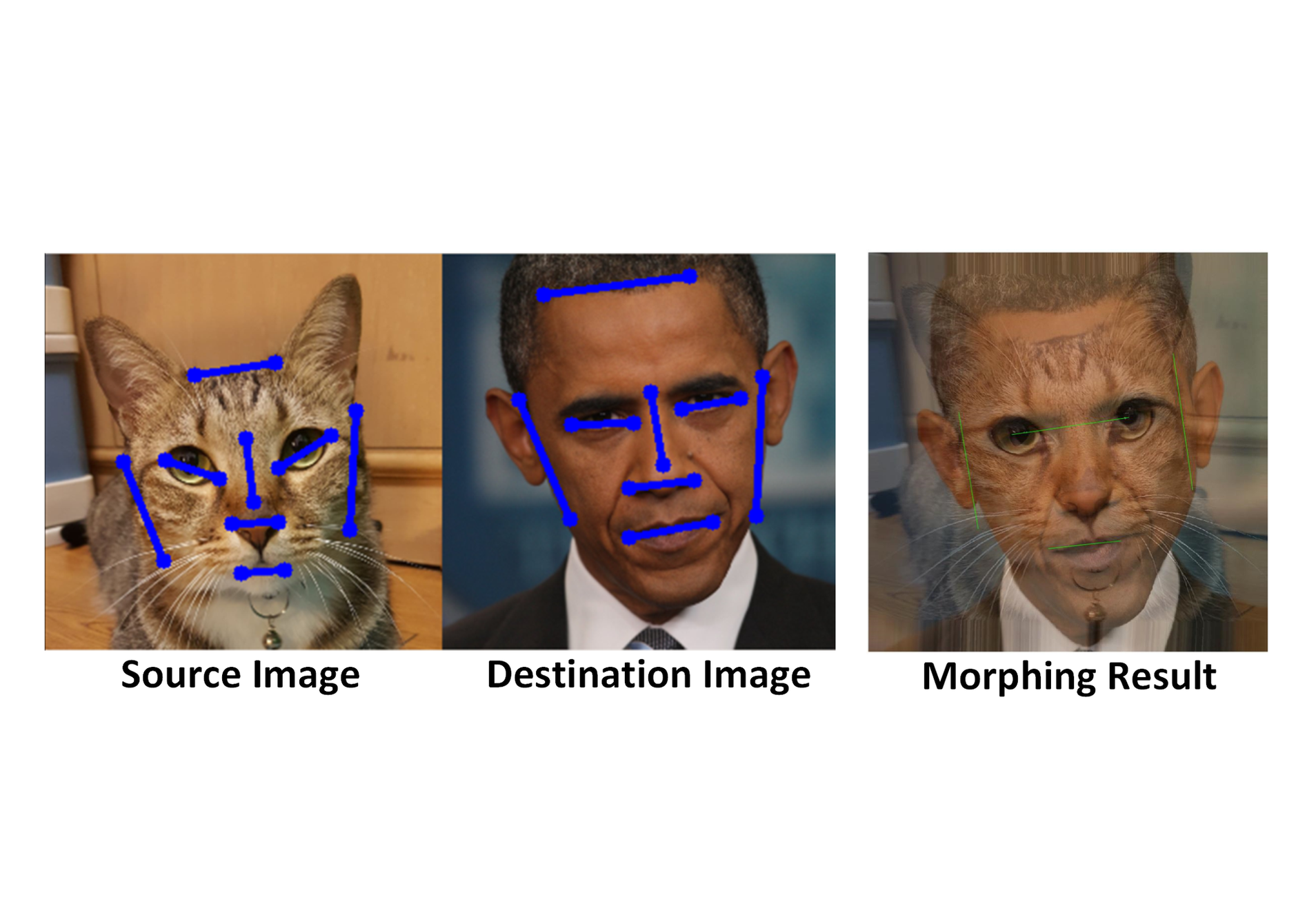

- Designed an accelerator for Beier-Nealy Algorithm

- Using Vivado High-Level Synthesis

- Ranked No.2 at the final project of Multimedia SoC Design

- Optimized the radix of Booth's Multiplier

- Conducted L2 Cache Analysis

- Final project of Digital System Design